МИР

ML на микроконтроллерах

ML на микроконтроллерах

Разработка алгоритмов

Дизайн моделей машинного обучения, например, нейросетей, оптимизированных с учетом специфики и ограничений микроконтроллеров.

Обучение, оптимизация и развертывание моделей

Обучение облегченных моделей и их развертывание на микроконтроллерах.

Аналитика данных

Разработка систем для анализа данных снимаемых с датчиков на устройствах на базе микроконтроллеров в режиме реального времени. Консультации по выбору подходящих датчиков и микроконтроллеров.

Решения Edge AI

Создание решений, в которых вычисления AI выполняются на периферии, на самом устройстве, а не в облаке. Оптимизация программного обеспечения и прошивки для маломощного и ограниченного по ресурсам оборудования.

Энергоэффективный ИИ

Выбор и оптимизация моделей машинного обучения для приложений с батарейным питанием.

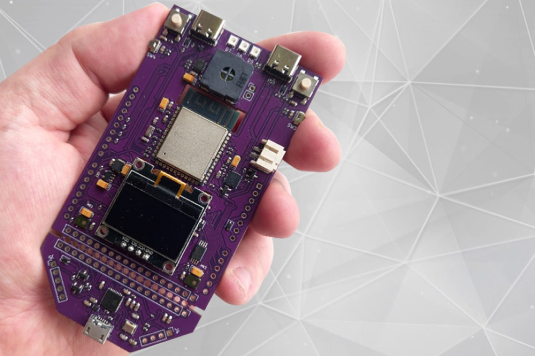

Разработка заказного оборудования

Дизайн индивидуальных плат микроконтроллеров, адаптированных для конкретных задач машинного обучения. Услуги по интеграции ML в существующие продукты и системы. Предоставление специализированных решений машинного обучения для устройств Интернета вещей.

Консультации и стратегия

Консультирование компаний по вопросам интеграции tinyML в их продукты и бизнес-стратегии.

Современное устройство, использующее алгоритмы искусственного интеллекта для распознавания уникального цифрового пин-кода, который произносит пользователь.

Отладочная плата размещается на корпусе любого вентилятора; в реальном времени обрабатывает поток данных с акселерометра для запоминания и дальнейшего определения режимов работы вентилятора или нестандартного состояния (аномалии).

Пользователь обучает плату своему ритму (постукиванием пальцем по корпусу платы). Ритм затем используется как персональный ключ.

Запоминает, а затем распознаёт 4 цифры пин-кода, произнесенные пользователем вслух.

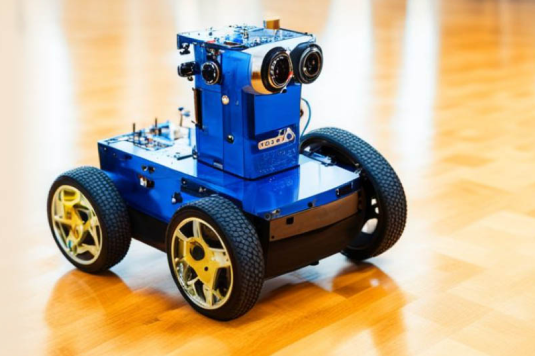

Для использования на движущихся механизмах по заданной траектории: промышленный манипулятор на конвейере, робо-рука. Размещается на корпусе манипулятора, запоминает «жесты», а затем, определяет его тип и сообщает об отклонениях.

В реальном времени обрабатывает поток данных с установленного на корпусе оборудования датчика вибрации.

Применяются алгоритмы искусственного интеллекта и локальное обучение на микроконтроллере с помощью рекуррентных нейросетей, которые выполняются прямо на устройстве, чтобы определить режим работы оборудования или то, что оно работает в неизвестном режиме (аномалия).

В отличие от «классического» ИИ не требует подготовки датасета и дорогостоящего предварительного обучения: обучается на устройстве в процессе работы.

Нормальные режимы работы оборудования записываются по команде пользователя.

Классификация нормального режима работы оборудования, а в случае неисправности — детекция аномального состояния.

При первом включении и после перезагрузки устройство готово запомнить ритм, который вводит пользователь. При появлении запроса дайте голосовую команду обучиться, и простучите свой ритм. После этого устройство перейдет в режим распознавания.

Устройство «прослушивает» входящий ритм и определяет, совпадает ли он с установленным. В случае совпадения устройство отправляет управляющий сигнал (например на реле для открытия двери), затем переходит в спящий режим.

В режиме ожидания устройство сохраняет энергию, ожидая команду от пользователя. Просыпание происходит по слову «Шейла», которое переводит устройство в режим распознавания или обучения.

Для готовых (обученных) NN’s

— Квантизация

— Прореживание, с контролем точности и времени исполнения

Уровень компилятора, учет специфики «железа»

— Распределение памяти

— Планировщик исполнения операций

— Разработка интринсиков

Рантайм

— Адаптация рантайм библиотеки

— Настройка планировщика исполнения операций

— Механизм профилировки (например, TVM Auto Scheduler)

— Низкоуровневая оптимизация бинарного кода (asm-level)

Цель — сделать устройства «умнее» и эффективнее, наблюдая за изменениями в текущем потоке собираемых данных и самостоятельно корректируя или переконфигурируя «операционную» модель устройства. При необходимости, «знания» полученные устройством, передаются другим развернутым в Edge устройствам.

Требования и ограничения:

— Лимитированная память для обучения

— Лимитированная память для буферизации данных

— Фиксированное время обучения нейросети

— Данные не могут сохранятся за произвольное время

— Максимально ограниченное взаимодействие с пользователем (оператором)

— Время обучения должно быть существенно меньше времени сбора данных

— Как правило, время обучения меньше секунды

Использование моделей машинного обучения (ML) на микроконтроллерах, по сравнению с традиционными алгоритмами, дает уникальные преимущества, особенно с учетом ограничений и особых требований.

Мгновенное принятие решений

Модели машинного обучения, развернутые на микроконтроллерах, могут принимать решения в режиме реального времени, что крайне важно для таких приложений, как робототехника, промышленность и устройства Интернета вещей, где необходима немедленная реакция.

Сокращение расходов на связь

Обрабатывая данные локально на микроконтроллере, модели машинного обучения уменьшают необходимость передачи данных в облачный сервер. Это снижает задержку и трафик, что критично при ограниченном интернете.

Энергоэффективность

Важно для устройств на батарейках.

Безопасность

Данные обрабатываются локально, решая задачу конфиденциальности.

Настраиваемость и гибкость

Модели машинного обучения можно подготовить специально для уникальных условий и требований окружения, в котором развернут микроконтроллер. Это позволяет создавать индивидуальные и гибкие решения по сравнению с универсальными традиционными алгоритмами.

Адаптивность

Модели могут со временем адаптироваться к изменениям в среде, улучшая свою производительность, или подстраиваться под новые типы данных без необходимости обновления традиционного алгоритма.

Обработка сложных сигналов

Модели машинного обучения лучше справляются со сложными нелинейными данными, которые традиционным алгоритмам сложно точно интерпретировать.

Масштабирование

После разработки модель можно развертывать на многочисленных устройствах без значительных дополнительных затрат, что дает экономическую эффективность.

Новые приложения

Создание решений, недостижимых традиционными методами, особенно в таких областях, как профилактическое обслуживание, мониторинг окружающей среды и устройства умного дома.

Однако важно учитывать и проблемы.

Реализация машинного обучения на микроконтроллерах часто связана с такими сложностями, как ограничения по памяти, вычислительной мощности и энергетических ресурсов.

Существует также сложность разработки и оптимизации моделей для эффективной работы на таких устройствах. Но с развитием искусственного интеллекта и подходов tinyML использование моделей машинного обучения в приложениях на базе микроконтроллеров становится все более доступным.

Адаптивность

Устройства могут обучаться и адаптироваться к новым данным в режиме реального времени, улучшая свои функции «на лету».

Скорость реакции

Быстрая обработка на устройстве устраняет задержку при отправке данных в облако для анализа.

Меньшее использование полосы пропускания

Отказ от передачи данных обеспечивает постоянную экономию полосы пропускания.

Энергоэффективность

Локальная обработка может быть менее энергозатратной, что критически важно для устройств с батарейным питанием.

Экономическая эффективность

Снижение затрат на хранение и обработку данных в облаке.

ООО «МИР»

194044, Санкт-Петербург,

ул. Гельсингфорсская, д.4.

ИНН 780465937

ОКВЭД: 62.01. Разработка компьютерного программного обеспечения